IEEE TRANSACTIONS ON SMART GRID, 2014

ABSTRACT

This paper proposes a new fault current limiting dynamic

voltage restorer (FCL-DVR) concept. The new topology uses a crowbar bidirectional

thyristor switch across the output terminals of a conventional back-to-back

DVR. In the event of a load short, the DVR controller will deactivate the

faulty phase of the DVR and activate its crowbar thyristor to insert the DVR filter

reactor into the grid to limit the fault current. A fault condition is detected

by sensing the load current and its rate of change. The FCL-DVR will operate

with different protection strategies under different fault conditions. Design

of the FCL-DVR involves selecting important parameters, such as DVR power

rating, dc link voltage of the DVR, output filter reactors and capacitors, and

grid-tied transformers is proposed. The design methodology of the proposed

FCL-DVR is fully discussed based on power systems computer aided design

(PSCAD)/electromagnetic transients including dc (EMTDC) simulation. A

scaled-down experimental verification is also carried out. Both modeling and

experimental results confirm the effectiveness of the new FCL-DVR concept for

performing both voltage compensation and fault current limiting functions.

KEYWORDS:

1.

Dynamic

voltage restorer (DVR)

2.

Fault current limiting

(FCL)

3.

Parameter

design method

4.

Voltage

compensation

SOFTWARE:

MATLAB/SIMULINK

CIRCUIT

DIAGRAM:

Fig. 1

Topology

of FCL-DVR.

EXPECTED SIMULATION

RESULTS:

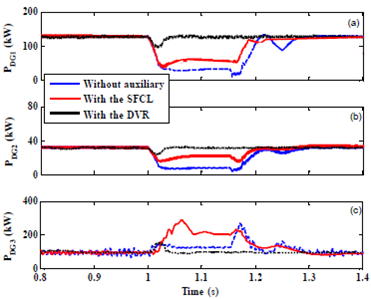

Fig

2. Simulation results of voltage compensation operation of FCL-DVR. Waveforms

of grid voltages, PCC voltages, load currents FCL-DVR output voltages, and dc

link voltages of the FCL-DVR during voltage fluctuation event and (b)

unbalanced voltage event.

CONCLUSION

A new FCL-DVR concept is proposed to deal with both voltage

fluctuation and short current faults. The new topology uses a crowbar

bidirectional thyristor switch across the output terminals of a conventional

back-to-back DVR. In the event of load short, the DVR controller will

deactivate the faulty phase of the DVR and activate its crowbar thyristor to

insert the DVR filter reactor into the grid to limit the fault current. The

FCL-DVR will operate with different protection strategies under different fault

conditions. Based on theoretical analysis, PSCAD/EMTDC simulation and

experimental study, we conclude the following.

1) With the crowbar bidirectional thyristor across

the output terminal of the inverter, the proposed FCL-DVR can compensate

voltage fluctuation and limit fault current.

2) The FCL-DVR can be used to deal with different

types of short faults with minimum influence on nonfault phases. The FCL-DVR

has the same power rating as a conventional DVR.

3) The delta-connection mode of the shunt

transformers minimizes the influence of dc link voltage fluctuations and

suppresses the 3rd harmonics.

4) The proposed control method can detect faults

within two cycles.

5) The design methodology based on the analysis of

the relationship between main circuit parameters and compensation capacity

could be helpful to the design of FCL-DVR.

REFERENCES

[1]

Z. Shuai et al., “A dynamic

hybrid var compensator and a two-level collaborative optimization compensation

method,” IEEE Trans. Power Electron., vol. 24, no. 9, pp. 2091–2100,

Sep. 2009.

[2]

L. Sainz, J. J. Mesas, R. Teodorescu,

and P. Rodriguez, “Deterministic and stochastic study of wind farm harmonic

currents,” IEEE Trans. Energy Convers., vol. 25, no. 4, pp. 1071–1080,

Dec. 2010.

[3]

F. Boico and B. Lehman, “Multiple-input

maximum power point tracking algorithm for solar panels with reduced sensing

circuitry for portable applications,” Solar Energy, vol. 86, no. 1, pp.

463–475, Jan. 2012.

[4]

R. F. Arritt and R. C. Dugan,

“Distribution system analysis and the future smart grid,” IEEE Trans. Ind.

Appl., vol. 47, no. 6, pp. 2343–2350, Nov. 2011.

[5]

U. Supatti and F. Z. Peng, “Z-source

inverter with grid connected for wind power system,” in Proc. Energy

Convers. Congr. Expo. (ECCE), San Jose, CA, USA, 2009, pp. 398–403.