ABSTRACT

In this paper speed of induction motor is controlled

which is fed from three phase bridge inverter. In this paper the speed of an

induction motor can be varied by varying input Voltage or frequency or both.

Variable voltage and variable frequency for Adjustable Speed Drives (ASD) is invariably

obtained from a three-phase Voltage Source Inverter (VSI). Voltage and frequency

of inverter can be easily controlled by using PWM techniques, which is a very

important aspect in the application of ASDs. A number of PWM techniques are

there to obtain variable voltage and variable frequency supply such as PWM,

SPWM, SVPWM to name a few, among the various modulation strategies SVPWM is one

of the most efficient techniques as it has better performance and output

voltage is similar to sinusoidal. In SVPWM the modulation index in linear region

will also be high when compared to other.

KEYWORDS

1.

Adjustable Speed Drive (ASD)

2.

Voltage source inverter (VSI)

3.

Sinusoidal PWM (SPWM)

4.

Space Vector PWM (SVPWM)

SOFTWARE:

MATLAB/SIMULINK

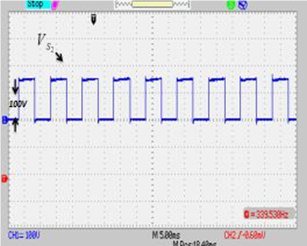

CIRCUIT DIAGRAM:

Figure

3 Motor Speed and Electromagnetic torque

CONCLUSION

The

simulation of “Control of Induction Motor Drive Using Space Vector PWM” is carried

out in MATLAB/Simulink. The simulation has been done for open loop as well as

closed control. The appropriate output results are obtained. The variation of

speed of Induction Motor has been observed by varying the load torque in open

loop control and results are noted down in the table. Also observed that for

the change in input speed commands the motor speed is settled down to its final

value within 0.1sec in closed loop model.

REFERENCES

[1] Abdelfatah Kolli, Student Member, IEEE,

Olivier Béthoux, Member, IEEE, Alexandre De Bernardinis, Member, IEEE, Eric Labouré,

and Gérard Coquery “Space-Vector PWM Control Synthesis for an H-Bridge Drive in

Electric Vehicles” IEEE TRANSACTIONS ON VEHICULAR TECHNOLOGY, VOL. 62, NO. 6,

JULY 2013. pp. 2241-2252.

[2] Mr. Sandeep N Panchal, Mr. Vishal S

Sheth, Mr. Akshay A Pandya “Simulation Analysis of SVPWM Inverter Fed Induction

Motor Drives” International Journal of Emerging Trends in Electrical and

Electronics (IJETEE) Vol. 2, Issue. 4, April-2013. pp. 18-22 .

[3] Haoran Shi, Wei Xu, Chenghua Fu and Yao

Yang. “Research on Threephase Voltage Type PWM Rectifier System Based on SVPWM

Control” Research Journal of Applied Sciences, Engineering and Technology

5(12): 3364-3371, 2013. pp. 3364-3371.

[4] K. Mounika, B. Kiran Babu, “Sinusoidal

and Space Vector Pulse Width Modulation for Inverter” International Journal of

Engineering Trends and Technology (IJETT) - Volume4Issue4- April 2013.

pp.1012-1017.

[5]

K. Vinoth Kumar, Prawin Angel Michael,

Joseph P. John and Dr. S. Suresh Kumar. “Simulation and Comparison Of Spwm And

Svpwm Control For Three Phase Inverter” ARPN Journal of Engineering and Applied

SciencesVOL. 5, NO. 7, JULY 2010. pp. 61-74.