ABSTRACT

In

this paper a XILINX FPGA based multilevel PWM single-phase inverter was

constructed by adding a bi-directional switchs to the conventional bridge

topology. The inverter can produce three and five different output voltage

levels across the load. XILINX FPGA is a programmable logic device developed by

XILINX which is considered as an efficient hardware for rapid prototyping. It

is used as a PWM generator to apply the appropriate signals to inverter

switches. In addition to XILINX FPGA, Matlab/Simulink software was used for

simulation and verification of the proposed circuit before implementation,

Simulation and experimental results show that both are in close agreement.

SOFTWARE: MATLAB/SIMULINK

CIRCUIT

DIAGRAM:

Fig.1 The proposed circuit of the multilevel PWM single phase

inverter

EXPECTED SIMULATION AND EXPERIMENTALRESULTS:

Fig.2.Multilevel PWM

single phase simulation results using XILINX FPGA at Ma = 0.8.

Fig.3 Multilevel PWM

single phase simulation results using XILINX FPGA at Ma = 0.4.

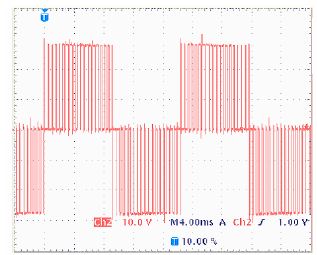

Fig.4 Multilevel single-phase PWM at Ma=0.8 Simulated, (b)

Experimental

Fig.5 Multilevel single-phase PWM at Ma=0.4 (a) Simulated,

(b) Experimental

Fig.6.Unfiltered output voltage five levels at Ma=0.8

Fig.7 Unfiltered output voltage five levels at Ma=0.4

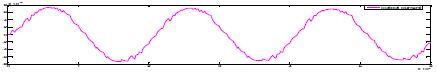

Fig.8. Ac voltage waveform before and after the filter in the proposed multilevel PWM inverter at modulationindexes (a) 0.8 and (b) 0.4.

Fig.9.Ac voltage and current output

waveforms for

resistive load.

Fig.10 Ac voltage and current output

waveforms for (resistive- inductive) load.

Fig.11Ac voltage output harmonic spectral after filter

CONCLUSION

The switching patterns adopted are applied at the six inverter

switches to generate five or three output voltage levels at different

modulation indexes. XILINX FPGA enables to make easy, fast and flexible design

and implementation. The experimental and simulated results are show

satisfactory results in term of total harmonic distortion and output voltage

and current waveform shapes.

REFERENCES

.

[1] V.G.Agelidis, D.M.Baker, W.B.Lawrance and C.V. Nayar “ AMultilevel

PWM Inverter Topology for Photovoltaic Applications” IEEE.ISIE’97,Guimaräes,

Portugal, pp.589-594, 1997.

[2] J.S. Lai and F.Z.Peng,

”Multilevel converters –A new breed of power conversion ” IEEE Trans. 1nd.

Applicat., vol.32, pp. 509-517, May/June. 1996.

[3] N.S. Choi, J.H. Cho, and G.H. Cho, “A General circuit Topology of

Multilevel Inverter” IEEE Trans. Power Electronics, vol. 6,

pp.96-103, 1991.

[4] E. Cengelci, S. U. Sulistijo, B. O. Woom, P. Enjeti, R.

Teodorescu, and F. Blaabjerge,“A new medium voltage PWM inverter topology for

adjustable speed drives” in Conf. Rec. IEEE-IAS Annu. Meeting, St. Louis

MO, pp.1416-1423, Oct.1998.

[5] B. N. Mwinyiwiwa,

Z.Wolanski, and B. T. Ooi, “Microp- rocessor implemented SPWM for

multiconverters with phase-shifted triangle carriers” in Conf. Rec IEEE-IAS

Annu. Meet- ing, NewOrleans, pp. 1542–1549, Oct. 1997.