ABSTRACT

This paper introduces and evaluates an auxiliary

control strategy for downstream fault current interruption in a radial distribution

line by means of a dynamic voltage restorer (DVR). The proposed controller

supplements the voltage-sag compensation control of the DVR. It does not

require phase-locked loop and independently controls the magnitude and phase

angle of the injected voltage for each phase. Fast least error squares digital

filters are used to estimate the magnitude and phase of the measured voltages

and effectively reduce the impacts of noise, harmonics, and disturbances on the

estimated phasor parameters, and this enables effective fault current

interrupting even under arcing fault conditions. The results of the simulation

studies performed in the PSCAD/EMTDC software environment indicate that the

proposed control scheme: 1) can limit the fault current to less than the

nominal load current and restore the point of common coupling voltage within 10

ms; 2) can interrupt the fault current in less than two cycles; 3) limits the

dc-link voltage rise and, thus, has no restrictions on the duration of fault

current interruption; 4) performs satisfactorily even under arcing fault

conditions; and 5) can interrupt the fault current under low dc-link voltage

conditions.

KEYWORDS

1. Digital

filters

2. Dynamic

Voltage Restorer (DVR),

3.

Fault current

interrupting,

4.

Multiloop

control.

SCHEMATIC

DIAGRAM

Fig. 1.

Schematic diagram of a DVR with a line-side harmonic filter

Fig. 2. Single-line diagram of the system used for simulation studies.

SIMULATION RESULTS

Fig. 3.

(a) Voltages at Bus3. (b) Fault currents, during downstream three-phase fault when the DVR is inactive (bypassed). Fig. 4. (a) Voltages at Bus3, (b) Fault currents, during downstream phase –tophase fault when the DVR is inactive (bypassed).

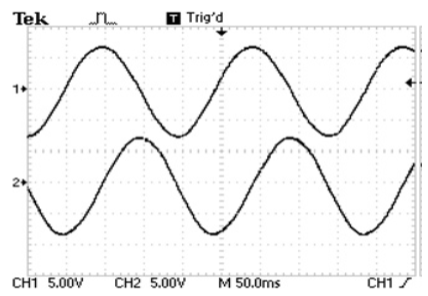

Fig.5 . (a) Injected voltages. (b) Source voltages. (c) Load voltages. (d) Line currents. (e) DC-link voltage, during the three-phase downstream fault.

Fig. 6.

(a) Voltages at Bus3. (b) Fault currents, during the downstream single phase-to-ground arcing fault

when the DVR is inactive (bypassed).

CONCLUSION

This

paper introduces an auxiliary control mechanism to enable the DVR to interrupt downstream

fault currents in a radial distribution feeder. This control function is an

addition to the voltage-sag compensation control of the DVR. The performance of

the proposed controller, under different fault scenarios, including arcing

fault conditions, is investigated based on time-domain simulation studies in

the PSCAD/EMTDC environment. The study results conclude that:

•

the proposed multiloop control system provides a desirable transient response

and steady-state performance and effectively damps the potential resonant

oscillations caused by the DVR LC harmonic filter;

• the proposed control system detects and

effectively interrupts the various downstream fault currents within two cycles (of

50 Hz);

• the proposed fault current interruption

strategy limits the DVR dc-link voltage rise, caused by active power

absorption, to less than 15% and enables the DVR to restore the PCC voltage without

interruption; in addition, it interrupts the downstream fault currents even

under low dc-link voltage conditions.

• the proposed control system also performs

satisfactorily under downstream arcing fault conditions.

REFERENCES

[1] N. G. Hingorani, “Introducing custom

power,” IEEE

Spectr., vol. 32, no. 6,

pp. 41–48, Jun. 1995.

[2] J. G. Nielsen, F. Blaabjerg, and N.

Mohan, “Control strategies for dynamic voltage restorer compensating voltage

sags with phase jump,” in Proc.

IEEE APEC’, 2001, pp.

1267–1273.

[3] G. J. Li, X. P. Zhang, S. S. Choi, T.

T. Lie, and Y. Z. Sun, “Control strategy for dynamic voltage restorers to

achieve minimum power injection without introducing sudden phase shift,” Inst. Eng. Technol. Gen. Transm. Distrib., vol. 1, no. 5, pp. 847–853, 2007.

[4] S. S. Choi, B. H. Li, and D. M.

Vilathgamuwa, “Design and analysis of the inverter-side filter used in the

dynamic voltage restorer,” IEEE Trans. Power Del., vol. 17, no. 3, pp. 857–864, Jul. 2002.

[5] B. H. Li, S. S. Choi, and D. M.

Vilathgamuwa, “Design considerations on the line-side filter used in the

dynamic voltage restorer,” Proc.

Inst. Elect. Eng., Gen. Transm.

Distrib., vol. 148, no. 1,

pp. 1–7, Jan. 2001.