ABSTRACT:

In this paper, a new three-phase, five-level

inverter topology with a single-dc source is presented. The proposed topology

is obtained by cascading a three-level flying capacitor inverter with a flying

H-bridge power cell in each phase. This topology has redundant switching states

for generating different pole voltages. By selecting appropriate switching

states, the capacitor voltages can be balanced instantaneously (as compared to

the fundamental) in any direction of the current, irrespective of the load

power factor. Another important feature of this topology is that if any H-bridge

fails, it can be bypassed and the configuration can still operate as a

three-level inverter at its full power rating. This feature improves the

reliability of the circuit. A 3-kW induction motor is run with the proposed

topology for the full modulation range. The effectiveness of the capacitor

balancing algorithm is tested for the full range of speed and during the sudden

acceleration of the motor.

KEYWORDS:

1.

Flying

capacitor (FC)

2.

H-bridge

3.

Induction motor drive

4.

Multilevel inverter

SOFTWARE: MATLAB/SIMULINK

CIRCUIT DIAGRAM:

Fig

1 Proposed three- phase power circuit formed by the connection of a three phase

flying capacitor inverter with H-bridge in series

EXPECTED SIMULATION RESULTS:

Fig. 2. Phase voltage VAN , phase current IA and capacitor voltage ripple for different modulation indexes for phase A: ∆VC 1 = 5 V/div; ∆VC 2 = 10 V/div;

IA = 2 A/div.

(a) 10 Hz with modulation index of 0.2 (VA N = 50 V/div,

time = 20 ms/div). (b) 20 Hz with modulation index of 0.4 (VAN = 100 V/div, time =10

ms/div). (c) 30 Hz with modulation

index of 0.6 (VAN = 100 V/div, time = 10 ms/div). (d) 40 Hz with modulation index of 0.8 (VA N = 100 V/div,

time = 5 ms/div).

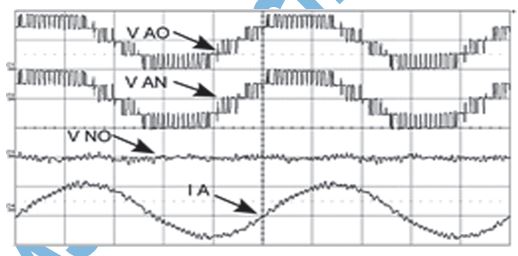

Fig. 3. Pole voltage VAO , phase current IA and capacitor voltage ripple for different modulation indexes for phase A: ∆VC 1 = 5 V/div; ∆VC 2 = 10 V/div;

IA = 2 A/div.

(a) 10 Hz with modulation index of 0.2 (VAO = 50 V/div, time = 20 ms/div). (b) 20 Hz with modulation index of

0.4 (VAO = 100 V/div,

time = 10 ms/div). (c) 30 Hz

with modulation index of 0.6 (VAO = 100 V/div,

and time = 10 ms/div). (d) 40 Hz with modulation index of 0.8 (VAO = 100 V/div, time = 5 ms/div).

Fig.

4. Rapid acceleration of motor from 10 to 40 Hz in 5.5 s. Capacitor voltage

remains constant. VAN (phase voltage): 200 V/div, IA (phase current): 2 A/div, VC 1 (VD C /2 capacitor DC voltage): 100 V/div, VC 2 (VD C /4 capacitor DC voltage): 100 V/div,

and time scale: 1 s/div.

Fig.

5. Capacitor balancing operation. The

balancing logic has been disabled at T1. C1 balancing has been enabled at T2

and C2 balancing has been en- abled at T3. VAN (phase voltage): 200 V/div, IA (phase

current): 2 A/div, VC 1(VD C /2 capacitor DC voltage): 100 V/div,

VC 2 (VD C /4 capacitor DC voltage): 100 V/div, and time scale: 2 s/div.

CONCLUSION:

In this paper, a new three-phase f ve-level inverter topology

with a single-dc source has been proposed.

This configuration is formed

by cascading a three-level FC inverter

and capacitor-fed H-bridges.

The key advantages of this topology

compared to the conventional topologies include reduced number of devices and simple control. An important

feature of this inverter is the ability

to balance the capacitor voltages irrespective of load power factor. Another advantage of this inverter is that if one of the H-bridge

fails, it can operate as a three-level inverter

at full power rating

by bypassing the H-bridge. This feature of the

inverter improves the reliability of

the system The proposed configuration

has been analyzed and experimentally verifie for various modulation indexes and

frequencies by running

a 3-kW squirrel cage induction motor in V/f control mode, at no load. The working of

the capacitor balancing algorithm has been tested. The stable operation of the inverter for various modulation indexes

and stability of the inverter voltage levels

during rapid acceleration have been

validated experimentally

REFERENCES:

[1]

L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, M.A.M. Prats,

“The age of multilevel

converters arrives,” IEEE

Ind. Electron. Magazine, vol. 2, no. 2, pp. 28–39,

June.2008.

[2]

S. Kouro, M.

Malinowski, K. Gopakumar,

J. Pou, L.

G. Franquelo, B.Wu, J. Rodriguez, M. A. Perez, and J. I.

Leon, “Recent Advances and Industrial Applications

of Multilevel Converters,” IEEE

Trans. Ind. Electron.,vol. 57, no. 8, pp.

2553–2580, Aug. 2010.

[3]

A. Nabae, I. Takahashi,

and H. Akagi, “A new

neutral-point-clamped PWM

inverter,” IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518–523, Sep. 1981.

[4]

M. Marchesoni, M. Mazzucchelli, and S. Tenconi, “A non-conventional power

converter for plasma

stabilization,” in Proc.

IEEE 19th Annu. Power

Electron. Spec. Conf. (PESC’88) Rec., Apr. 11–14,

vol. 1, pp. 122–129.

[5]

Z. Du,

L.M. Tolbert, J. N. Chiasson,

B. Ozpineci, H. Li, and

A. Q. Huang,

“Hybrid cascaded H-bridges

multilevel motor drive control for electric

vehicles,” in Proc. IEEE 37th Power Electron. Spec. Conf., Jun. 18–22, 2006, pp. 1–6.